作者: 雷火电竞首页 来源: 日期:2024-07-13 12:46

现场可编程逻辑门阵列芯片是一种可重构的半定制集成电路,可以根据用户的需求进行硬件编程,从而实现特定的功能。

北京大学发布面向大规模FPGA芯片的布局布线开源框架OpenPARF

现场可编程逻辑门阵列芯片是一种可重构的半定制集成电路,可以根据用户的需求进行硬件编程,从而实现特定的功能。FPGA主要用于数字信号处理、通信、嵌入式系统、图像和视频处理、网络加速、人工智能等多个领域,拥有广阔的应用。

在过去的十年里,随着半导体制造工艺不断发展,业界逐步提高FPGA芯片的集成化和系统化,加入了大量的高速运算单元、内存层次资源、领域专用加速器等。集成化和系统化对FPGA芯片设计的EDA工具提出了更大的挑战,如何提高其EDA工具的性能、效率和灵活性,以适应多样化的片上计算资源,成为FPGA应用的瓶颈之一。

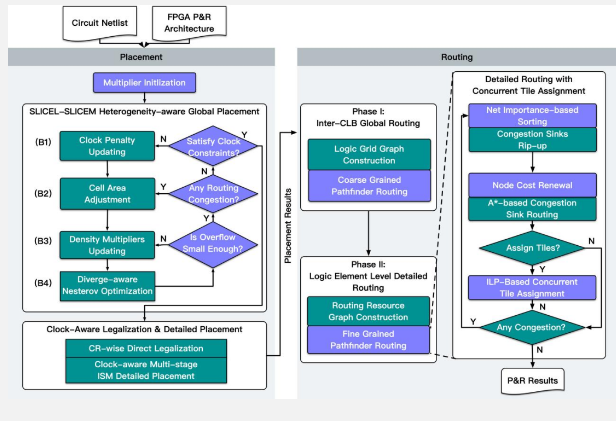

为了实现这一目标,北京大学集成电路学院设计自动化与计算系统系/无锡北京大学EDA研究院林亦波团队发布了面向大规模FPGA芯片的布局布线开源框架OpenPARF。其主要特点如下:

高质量。

OpenPARF集成了当前学术界最先进的布局布线算法,能在大规模FPGA芯片上完成布局布线任务,求解质量和运行效率达到国际领先水平。

高性能。OpenPARF充分挖掘算法并行性,利用GPU实现异构并行加速,相较传统工具能大幅减少布局布线的运行时间。

与深度学习工具相结合。

OpenPARF基于深度学习框架PyTorch 实现,使用C++/CUDA/Python混合编程,兼具C++/CUDA的高效性和Python的灵活性,代码灵活易上手,方便集成人工智能算法。

OpenPARF框架示意图

本工作受到国家自然科学基金重大项目“高效率、高可靠性设计的EDA新理论与新方法”等项目的支持,受邀将于IEEE ASICON 2023做特邀报告进行详细介绍。

该框架的愿景是建立一个芯片设计与人工智能结合的开放生态平台,为工业界和学术界探索和开发下一代高性能FPGA布局布线算法提供支撑,从而进一步推动芯片设计和人工智能的研究发展。

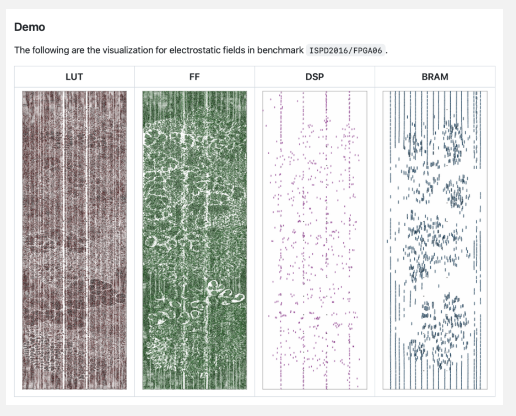

OpenPARF布局求解过程示意图

。本文来源:雷火电竞首页-www.sdsaigeyiqi.com